gf180mcu_fd_sc_mcu7t5v0__dffq_2¶

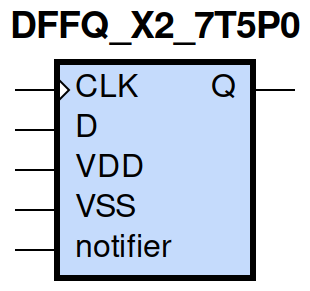

gf180mcu_fd_sc_mcu7t5v0__dffq_2 symbol

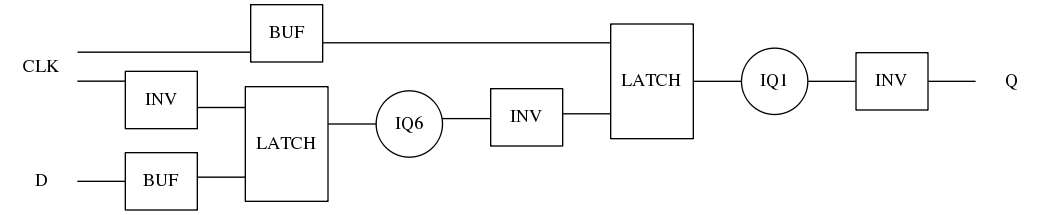

gf180mcu_fd_sc_mcu7t5v0__dffq_2 schematic

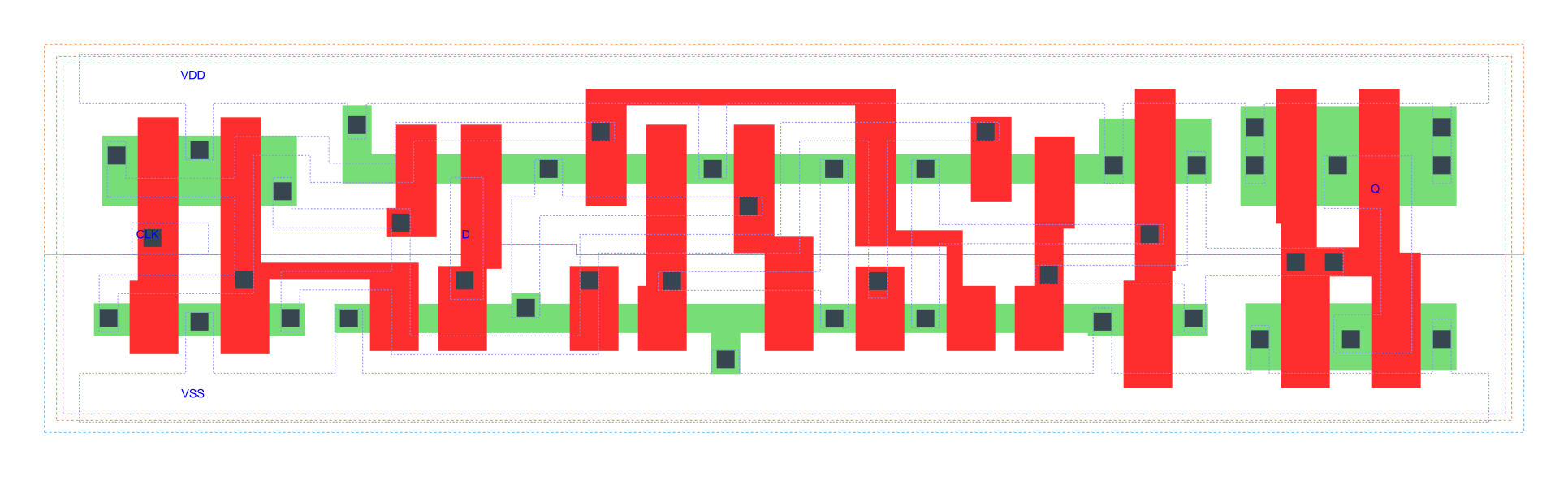

gf180mcu_fd_sc_mcu7t5v0__dffq_2 layout

DFFQ_X2 is a poistive edge triggered D-type flip flop, 2X drive strength

Attribute |

Value |

area |

68.051200 µm2 |

TRUTH TABLE

Input |

Output |

|

D |

CLK |

Q |

L |

↑ |

L |

H |

↑ |

H |

Constraint Pin |

Related Pin |

setup(ns) |

hold(ns) |

D(LH) |

CLK(LH) |

0.2350 |

0.0460 |

D(HL) |

CLK(LH) |

0.2350 |

0.0920 |

Constraint Pin |

Related Pin |

Minimum Pulse Width(ns) |

CLK(LHL) |

CLK(LH) |

0.3100 |

CLK(LHL) |

CLK(LH) |

0.5540 |

CLK(HLH) |

CLK(HL) |

0.5590 |

CLK(HLH) |

CLK(HL) |

0.3760 |

Pin |

Type |

Capacitance (pf) |

CLK |

input |

0.0032 |

D |

input |

0.0024 |

Input Pin |

Output |

When Condition |

Tin (ns) |

Out Load (pf) |

Delay (ns) |

Tout (ns) |

CLK(LH) |

Q(HL) |

!D |

0.0100 |

0.0010 |

0.6358 |

0.0398 |

CLK(LH) |

Q(LH) |

D |

0.0100 |

0.0010 |

0.7275 |

0.0429 |

Input Pin |

When Condition |

Tin (ns) |

Output |

Out Load (pf) |

Energy (uW/MHz) |

CLK |

!D |

0.0100 |

Q(HL) |

0.0010 |

0.6237 |

CLK |

D |

0.0100 |

Q(LH) |

0.0010 |

0.6252 |

D(LH) |

!CLK |

0.0100 |

n/a |

n/a |

0.1085 |

D(LH) |

CLK |

0.0100 |

n/a |

n/a |

-0.0067 |

CLK(LH) |

!D |

0.0100 |

n/a |

n/a |

0.2146 |

CLK(LH) |

D |

0.0100 |

n/a |

n/a |

0.2141 |

D(HL) |

!CLK |

0.0100 |

n/a |

n/a |

0.1615 |

D(HL) |

CLK |

0.0100 |

n/a |

n/a |

0.0097 |

CLK(HL) |

!D |

0.0100 |

n/a |

n/a |

0.2837 |

CLK(HL) |

D |

0.0100 |

n/a |

n/a |

0.2878 |

When Condition |

Power (nW) |

!CLK&!D |

0.3747 |

!CLK&D |

0.4002 |

CLK&!D |

0.4670 |

CLK&D |

0.4946 |