gf180mcu_fd_sc_mcu7t5v0__dlyb_4¶

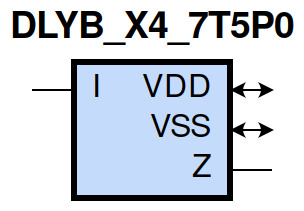

gf180mcu_fd_sc_mcu7t5v0__dlyb_4 symbol

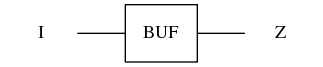

gf180mcu_fd_sc_mcu7t5v0__dlyb_4 schematic

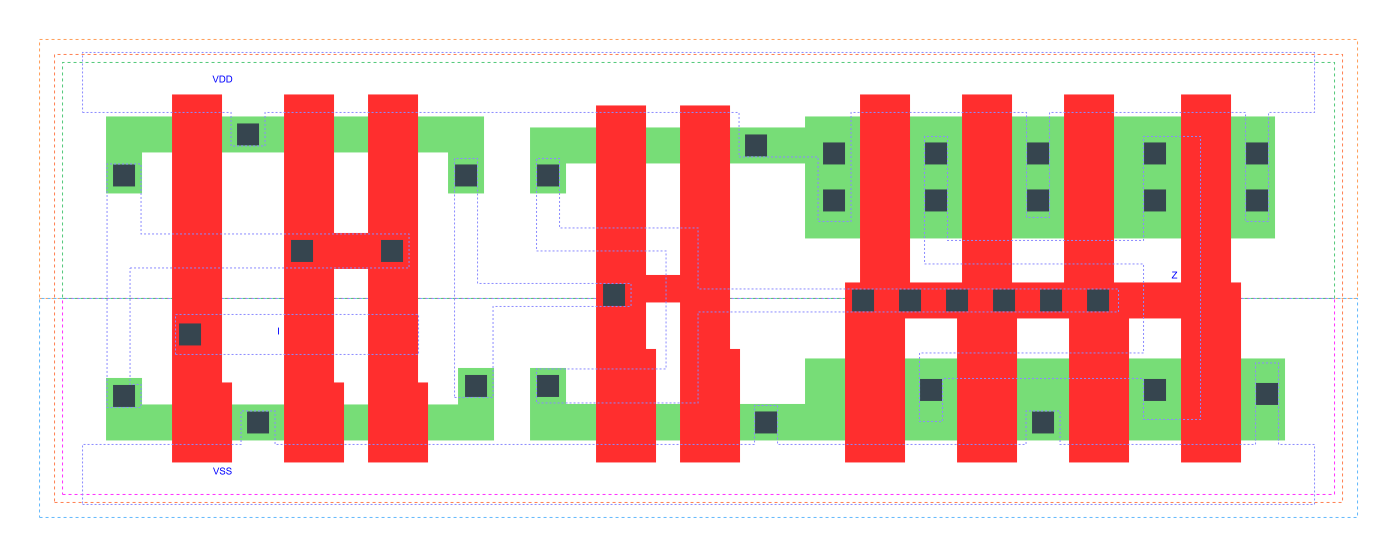

gf180mcu_fd_sc_mcu7t5v0__dlyb_4 layout

DLYB_X4 is a 4 buffer delay cell, 4X drive strength

Attributes

Attribute |

Value |

area |

48.294400 µm2 |

OUTPUT FUNCTIONS

Output Pin |

Function |

Z |

I |

TRUTH TABLE FOR Z

I |

Z |

1 |

1 |

0 |

0 |

FUNCTIONAL SCHEMATIC

PIN CAPACITANCE (pf)

Pin |

Type |

Capacitance (pf) |

I |

input |

0.0028 |

DELAY AND OUTPUT TRANSITION TIME corresponding to min slew and load

Input Pin |

Output |

When Condition |

Tin (ns) |

Out Load (pf) |

Delay (ns) |

Tout (ns) |

I(LH) |

Z(LH) |

default |

0.0100 |

0.0010 |

1.1058 |

0.0722 |

I(HL) |

Z(HL) |

default |

0.0100 |

0.0010 |

1.4644 |

0.1558 |

DYNAMIC ENERGY

Input Pin |

When Condition |

Tin (ns) |

Output |

Out Load (pf) |

Energy (uW/MHz) |

I |

default |

0.0100 |

Z(LH) |

0.0010 |

1.0214 |

I |

default |

0.0100 |

Z(HL) |

0.0010 |

2.0871 |

LEAKAGE POWER

When Condition |

Power (nW) |

!I |

0.2351 |

I |

0.2293 |