gf180mcu_fd_sc_mcu9t5v0__dffq_1¶

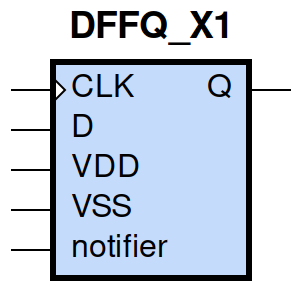

gf180mcu_fd_sc_mcu9t5v0__dffq_1 symbol

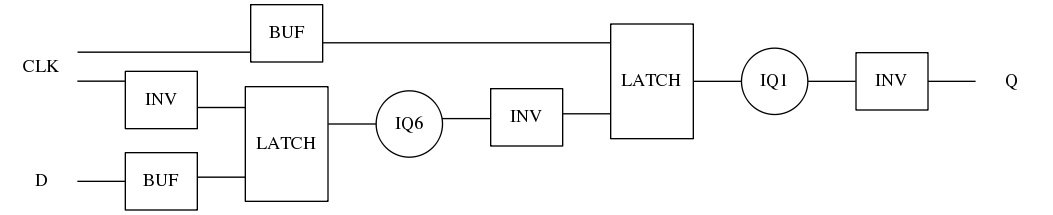

gf180mcu_fd_sc_mcu9t5v0__dffq_1 schematic

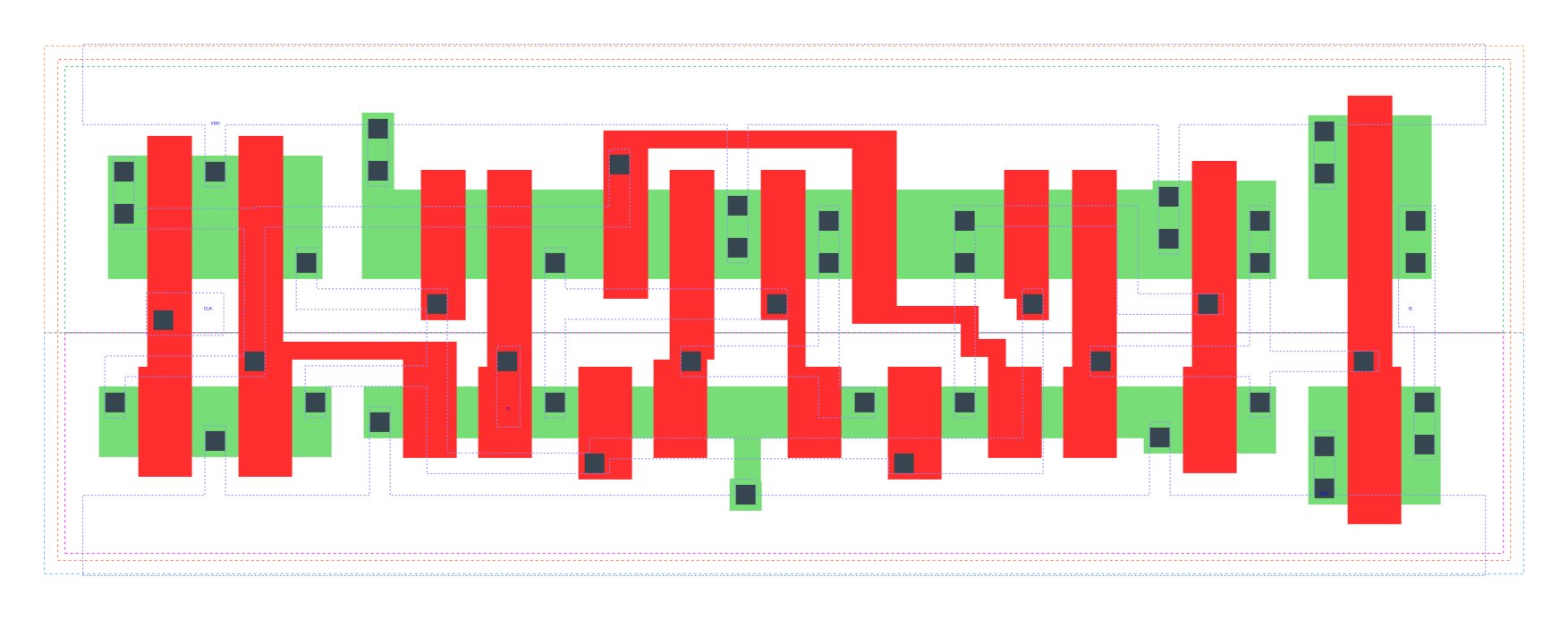

gf180mcu_fd_sc_mcu9t5v0__dffq_1 layout

Attribute |

Value |

area |

79.027200 µm2 |

TRUTH TABLE

Input |

Output |

|

D |

CLK |

Q |

L |

↑ |

L |

H |

↑ |

H |

Constraint Pin |

Related Pin |

setup(ns) |

hold(ns) |

D(LH) |

CLK(LH) |

0.1830 |

0.0110 |

D(HL) |

CLK(LH) |

0.1370 |

0.1090 |

Constraint Pin |

Related Pin |

Minimum Pulse Width(ns) |

CLK(LHL) |

CLK(LH) |

0.2710 |

CLK(LHL) |

CLK(LH) |

0.3100 |

CLK(HLH) |

CLK(HL) |

0.3940 |

CLK(HLH) |

CLK(HL) |

0.3150 |

Pin |

Type |

Capacitance (pf) |

CLK |

input |

0.0050 |

D |

input |

0.0038 |

Input Pin |

Output |

When Condition |

Tin (ns) |

Out Load (pf) |

Delay (ns) |

Tout (ns) |

CLK(LH) |

Q(HL) |

!D |

0.0100 |

0.0010 |

0.5297 |

0.0354 |

CLK(LH) |

Q(LH) |

D |

0.0100 |

0.0010 |

0.4865 |

0.0364 |

Input Pin |

When Condition |

Tin (ns) |

Output |

Out Load (pf) |

Energy (uW/MHz) |

CLK |

!D |

0.0100 |

Q(HL) |

0.0010 |

0.6822 |

CLK |

D |

0.0100 |

Q(LH) |

0.0010 |

0.6376 |

D(LH) |

!CLK |

0.0100 |

n/a |

n/a |

0.1550 |

D(LH) |

CLK |

0.0100 |

n/a |

n/a |

-0.0240 |

CLK(LH) |

!D |

0.0100 |

n/a |

n/a |

0.2611 |

CLK(LH) |

D |

0.0100 |

n/a |

n/a |

0.2603 |

D(HL) |

!CLK |

0.0100 |

n/a |

n/a |

0.2291 |

D(HL) |

CLK |

0.0100 |

n/a |

n/a |

0.0223 |

CLK(HL) |

!D |

0.0100 |

n/a |

n/a |

0.3959 |

CLK(HL) |

D |

0.0100 |

n/a |

n/a |

0.4088 |

When Condition |

Power (nW) |

!CLK&!D |

0.3461 |

!CLK&D |

0.3876 |

CLK&!D |

0.4899 |

CLK&D |

0.5995 |