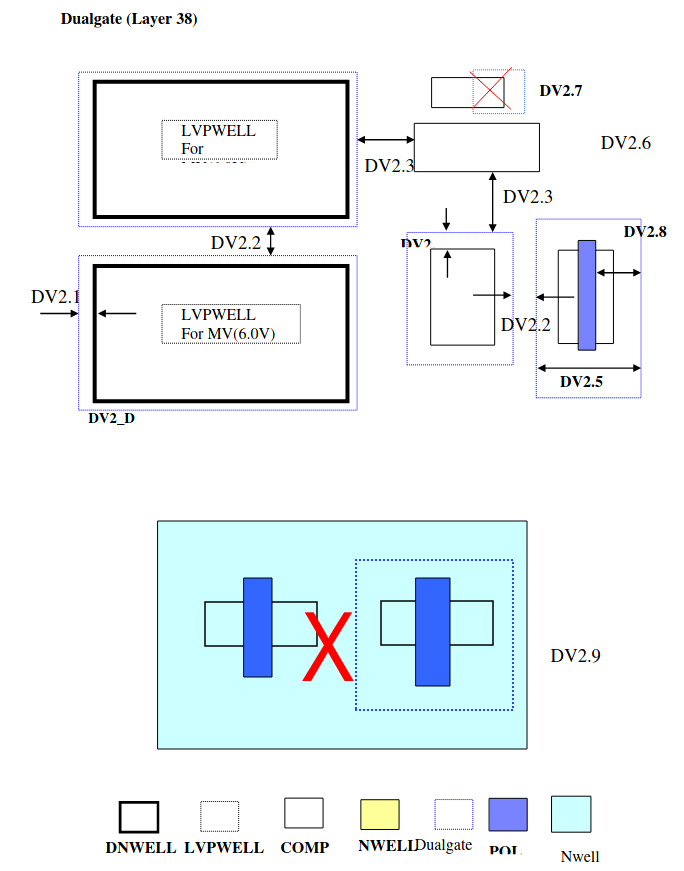

7.6 Dualgate¶

This layer defines the 5V/6V area. All 5V/6V device area should be covered by this layer.

RULE NO. |

DESCRIPTION |

LAYOUT RULE |

Layer |

DV = Dual Voltage = Dualgate |

|

DV.1 |

Min. Dualgate enclose DNWELL |

0.5 |

DV.2 |

Min. Dualgate Space. Merge if Space is less than this design rule. |

0.44 |

DV.3 |

Min. Dualgate to COMP space [unrelated] |

0.24 |

DV.4* |

Circuits covered by Dualgate layer will have 5V/6V gate oxide for 5V/6V operation. |

Rules specific to 3.3V/(5V)6V Dualgate outside DNWELL:

RULE NO. |

DESCRIPTION |

LAYOUT RULE |

DV.5 |

Min. Dualgate width |

0.7 |

DV.6 |

Min. Dualgate enclose COMP (except substrate tap) |

0.24 |

DV.7 |

COMP (except substrate tap) can not be partially overlapped by Dualgate |

|

DV.8 |

Min Dualgate enclose Poly2 |

0.4 |

DV.9 |

3.3V and 5V/6V PMOS cannot be sitting inside same NWELL |